# Design of a Digitized Vibration Detector Implemented by CMOS Digitized Capacitive Transducer With In-Plane SoI Accelerometer

Cheng-Ta Chiang, Senior Member, IEEE, Chun-I Chang, and Weileun Fang, Senior Member, IEEE

Abstract-In this paper, a digitized vibration detector implemented by CMOS digitized capacitive transducer with in-plane silicon-on-insulator (SoI) accelerometer is newly proposed. The proposed digitized vibration detector is attractive due to the fact that all the circuits and the sensor can be robustly and compactly combined together. A total solution including the continuous-time-voltage (CTV) analog sensing circuits and digitalized interface are proposed in this paper. Based upon 0.35-µm 2P4M CMOS technology with 3 V power supply, all the functions and performance of the proposed CMOS digitized capacitive transducer are successfully tested and proven through measurements and confirmed it to be applied on the in-plane SoI accelerometer. The sensitivity of the proposed CTV analog sensing circuits is 50.488 mV/g and maximum nonlinearity is 2.5% over the excitation of 0.25-5.75-g intensity. The peak signalto-noise-plus-distortion ratio of the proposed digitized vibration detector is 67.6 dB under excitation of 3.25-g intensity. The proposed digitized vibration detector is suitable for digitized accelerometer applications, such as automobiles, consumer electronics, Wii game player, and so on.

*Index Terms*—Sensor interface, accelerometer, sensor transducer, CMOS, capacitive sensor.

# I. INTRODUCTION

**N** OWADAYS, MEMS (Micro Electro Mechanical Systems) accelerometers play an increasing role in applications as automobiles, navigation, vibration monitoring, and portable consumer electronics. Thus, the commercial market of accelerometers is rapidly increased. Presently, there are various accelerator designs have been reported, such as capacitance [1]–[11], piezoresistive [12], piezoelectric [13], [14], optics [15], and tunneling [16] types. For the accelerators, the corresponding readout circuits are also important. By following the characteristics of accelerators, readout circuits can be grouped into piezoelectric, piezoresistive, capacitive types,

Manuscript received January 9, 2014; accepted January 27, 2014. Date of publication January 29, 2014; date of current version June 26, 2014. This work was supported by the National Chip Implementation Center of Taiwan for chip fabrication. This work was also supported by the National Science Council, Taiwan, under contracts NSC-102-2221-E-415-025. The associate editor coordinating the review of this paper and approving it for publication was Prof. Zeynep Celik-Butler.

C.-T. Chiang is with the Department of Electrical Engineering, National Chia Yi University, Chiayi 600, Taiwan (e-mail: ctchiang@mail.ncyu.edu.tw).

C.-I Chang and W. Fang are with the Department of Power Mechanical Engineering, National Tsing Hua University, Hsinchu 300, Taiwan (e-mail: fang@pme.nthu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSEN.2014.2303646

and etc. Among them, capacitive interfaces have the advantage of easily being integrated with CMOS MEMS sensors. Previous achievements related to the interface of capacitive accelerometers [17]-[32] had been demonstrated. However, sensing methods of these circuit structures are different. [17]–[22] are based on continuous-time-voltage sensing technique, and [23]-[32] are followed by switch-capacitor (SC) charge integration. Comparing these two sensing methods, the CTV sensing technique has the lower noise floor than SC charge integration [18]. Thus, analog sensing circuits of this work are wholly developed by following the CTV method. In order to consider for commercial market, a digitized output feature is also needed. The digitized output should be a bit stream, it could thus be easily sent over a wide range of transmission media, such as PSN, radio, optical, IR, ultrasonic, and etc. Besides, the sensing signal can not be easily affected by noise at low frequency band. Therefore, in order to fit to the requirements discussed above, a set of suitable CTV analog sensing circuits with digitalized interface is designed in this work. Although previous works [17]-[22] followed by the CTV method have been excellently presented, a total solution including the CTV analog sensing circuits and digitalized interface have not completely discussed yet. A table of comparisons to previously published designs is listed in Table I. Readers can understand the whole design techniques from this work, and this is the main contribution of this work.

In this work, a digitized vibration detector implemented by CMOS digitized capacitive transducer with in-plane SOI accelerometer is newly proposed. The area of the proposed CMOS digitized capacitive transducer is  $1812 \times 1420 \ \mu m^2$ and the power consumption including digital buffers is 18 mW. The sensitivity of the proposed CTV analog sensing circuits is 50.488 mV/g and maximum nonlinearity is 2.5% over the excitation of 0.25 to 5.75g intensity. The noise floor is 0.922 mg/Hz<sup>1/2</sup>. The cross-axis Y sensitivity and crossaxis Z sensitivity are less than 1.7% and 1.66%, respectively. The peak signal-to-noise-plus-distortion ratio of the proposed digitized vibration detector is 67.6 dB under excitation of 3.25g intensity. The effective resolution is equal to 11 bits. The proposed digitized vibration detector is suitable for digitized accelerometer applications, such as automobiles, consumer electronics, Wii game player, etc.

In section II, the capacitive in-plane SOI accelerometer is addressed. The system architecture and simulation results are described in section III. In section IV, measurement results are

1530-437X © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

|                         | [17]             | [18]             | [19]                 | [21]             | [22]             | This work            |

|-------------------------|------------------|------------------|----------------------|------------------|------------------|----------------------|

| Sensor                  | Surface          | Surface          | 0.35 μm              | 0.35 μm          | 0.35 μm          | SOI                  |

| Technology              | micromachined    | micromachined    | CMOS                 | CMOS             | CMOS             | process              |

|                         | technology with  | technology       | process              | process          | process          |                      |

|                         | integrated       | with integrated  |                      |                  |                  |                      |

|                         | 2 μm CMOS        | 0.5 μm CMOS      |                      |                  |                  |                      |

| Sensing<br>method       | сту              | сту              | сту                  | сту              | сту              | сту                  |

| Sensing<br>Range        | ±50 g            | ±6 g             | ±l g                 | ±11.5 g          | ±2 g             | 0.25-5.75g           |

| Maximum<br>sensitivity  | N.A.             | 130 mV/g         | 520 mV/g             | 144<br>mV/g      | 457<br>mV/g      | 50.488<br>mV/g       |

| Maximum<br>nonlinearity | N.A.             | N.A.             | N.A.                 | N.A.             | 1.28%            | 2.5%                 |

| Whole                   | 110              | 50               | 110                  | 130              | 54               | 922                  |

| noise floor             | $\mu g/Hz^{1/2}$ | $\mu g/Hz^{1/2}$ | μg/Hz <sup>1/2</sup> | $\mu g/Hz^{1/2}$ | $\mu g/Hz^{1/2}$ | μg/Hz <sup>1/2</sup> |

| Output<br>type          | Analog           | Analog           | Analog               | Analog           | Analog           | Digital              |

TABLE I

Comparisons to Previously Published Designs

shown and discussed. Finally, section V gives conclusions and future works.

#### II. CAPACITIVE IN-PLANE SOI ACCELEROMETER

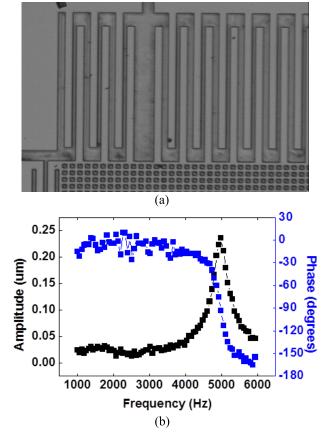

The microphotograph and measured results of the capacitive in-plane SOI accelerometer [11] are shown in Fig. 1. The measured resonant frequency is 4.987 kHz. Fabrication of MEMS devices using an SOI wafer has advantages. Firstly, it has the superior material properties due to a single crystal material. Using SOI techniques, thick devices are easily achieved. Finally, it can have less residual stresses and simple fabrication processes. The implementation of inertial sensors by using an SOI wafer has been increased [4], [6], [11], [25], [28], [30]. More detailed specification information and sensor model of the in-plane SOI accelerometer can be referred to [11]. In the section IV, the measured in-plane SOI accelerometer is experimented on the proposed CMOS digitized capacitive transducer. In the following sections, all the discussions of system architecture, simulations, and measurement results are completely discussed.

## **III. SYSTEM ARCHITECTURE AND SIMULATION RESULTS**

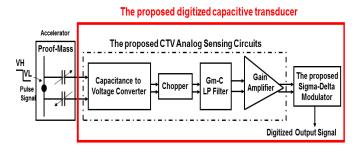

Fig. 2 shows the block diagram of the proposed CMOS digitized capacitive transducer, which consists of the capacitance to voltage converter (CVC), the demodulated chopper, Gm-C low-pass filter, gain amplifier, and the 4-stage sigma-delta modulator. All the circuit structures are discussed in this section clearly.

## A. Capacitance to Voltage Converter and Gain Amplifier

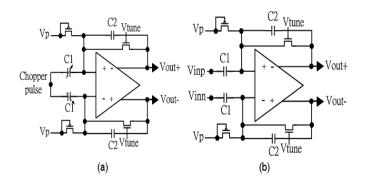

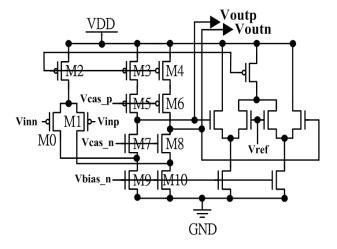

According to the principle of the charge conservation, any capacitance variations will also affect the corresponding voltage value. When the vibration makes the accelerator change its capacitance, a voltage signal is generated at the same time. Based on this principle, the proposed CTV analog sensing circuits are thus designed. Fig. 3 shows the circuit

Fig. 1. The (a) microphotograph (b) measured resonant frequency of the in-plane SOI accelerometer. The resonant frequency is 4.987 kHz.

Fig. 2. The block diagram of the proposed CMOS digitized capacitive transducer.

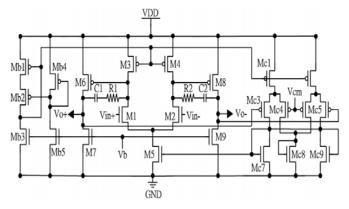

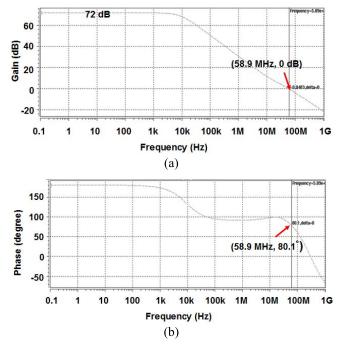

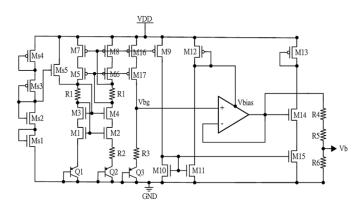

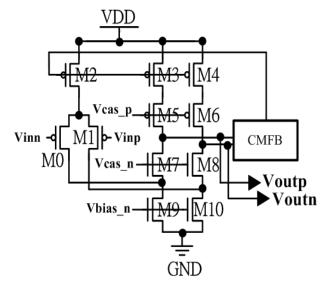

schematic of the capacitance to voltage converter and gain amplifier. The main difference between them is the value of the capacitance  $C_1$  and  $C_2$ . In Fig. 3(a), the  $C_1$  is the nominal capacitance of the accelerator and  $C_2$  is designed as a fixed capacitance of 200 fF. Due to the post-process variation, the nominal capacitance of the  $C_1$  is generally varied between 200 to 600 fF, and the minimum and maximum capacitance of the  $\Delta C$  is varied between 0.001 to 0.2% of the nominal capacitance. For the gain amplifier shown in Fig. 3(b), the  $C_1$  and  $C_2$  are designed 1.1 pF and 50 fF, respectively. The operational amplifier (OP) used in the CVC and gain amplifier is shown in Fig. 4. For gain amplifier, the OP performance over the frequency range from 0.1 Hz to 1 GHz is illustrated in Fig. 5. The DC gain is 72 dB, the unit gain bandwidth is 58.9 MHz, and the phase margin is 80.1°. The noise power of

Fig. 3. The circuit schematic of the (a) capacitance to voltage converter and (b) gain amplifier.

Fig. 4. The circuit schematic of the operational amplifier used in the CVC and gain amplifier.

Fig. 5. SPICE simulation results of the operational amplifier over the frequency range from 0.1 Hz to 1 GHz (a) gain and (b) phase response.

the flicker noise (1/f noise) of the OP is expressed as

$$\bar{V}n^2 = \frac{K}{C_{OX}WL}\frac{1}{f}\Delta f \tag{1}$$

Fig. 6. The circuit schematic of the bias circuit built from the bandgap reference.

Fig. 7. The circuit schematic of the demodulated chopper.

where *K* is a process dependent constant and is on the order of  $10^{-25}$  V<sup>2</sup>F,  $C_{OX}$  is the capacitance per unit area of the gate oxide and is on the order of 10 fF/ $\mu$ m<sup>2</sup>, and *W* and *L* are the dimensions of the transistors in the input stage. Analyzing from (1), the noise power can be reduced by making the sizes of the transistors (i.e.  $M_1$  and  $M_2$ ) larger. In the specification the resolution of the preamplifier is 10 bits. The noise needs to be less than 1 LSB. The integral noise power is expressed as

$$\sqrt{\int_{20}^{20k} \frac{K}{C_{ox}WL} \frac{1}{f}} \le \frac{Vi}{2^{10}}$$

(2)

where  $V_i$  is the input signal and is on the order of 10  $\mu$ V. By performing SPICE simulations, the flicker noise is integral over the frequency range from 20 Hz to 20 kHz. Thus, W and L are obtained. In order to avoid the effect of the temperature variations, the bias circuit is built with a bandgap reference and demonstrated in Fig. 6. The output voltage of the bias circuit is expressed as

$$V_b = \left(\frac{I_{16}}{I_8} \frac{R_3}{R_2} V_T * \ln n + V_{BE3}\right) * \frac{R_6}{R_4 + R_5 + R_6}$$

(3)

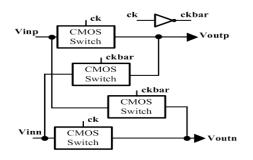

where  $V_T$  is kT/q,  $I_{16}$  and  $I_8$  is the currents of MOS  $M_{16}$  and  $M_8$ ,  $V_{BE3}$  is the base-emitter voltage of bipolar transistor (BJT)  $Q_3$ , and *n* is the ratio of collector currents between the BJT  $Q_2$  and  $Q_1$ . In order to avoid interference by noise, chopping modulation principle is used. As shown in Fig. 2, the proof mass of the accelerator is chopped with a pulse signal. The sensing signal and noise at low frequency band are moved into high frequency band together. By performing the demodulated chopper as shown in Fig. 7,

Fig. 8. The circuit schematic of the Gm-C low-pass filter.

Fig. 9. The circuit schematic of the Gm cell.

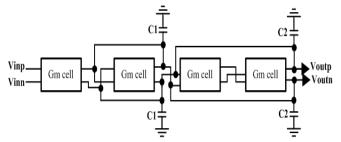

the sensing signal is moved into its original frequency band. However, noise remains to stay at the high frequency band. After the demodulated chopper, a low-pass filter is required to select the sensing signal and filter out the unwished signals, such as noise. The block scheme of the low-pass filter is designed with the  $2^{nd}$  order Gm-C structure as shown in Fig. 8. The transfer function is derived as

$$\frac{Voutn - Voutp}{Vinn - Vinp} = \frac{gm^2}{s^2 C_1 C_2 + s C_2 gm + gm^2}$$

(4)

$$\omega_0 = \frac{gm}{\sqrt{C_1 C_2}}, \quad Q = \sqrt{\frac{C_1}{C_2}} \tag{5}$$

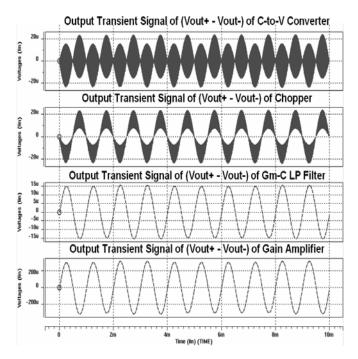

where gm is the transconductance of the Gm cell demonstrated in Fig. 9, Q the quality factor of the filter,  $\omega_0$  the cutoff frequency of the filter. When the transconductance is designed well, the cut-off frequency can be easily adjusted by changing the  $C_1$  or  $C_2$ . All the circuit blocks are integrated and grouped as the proposed CTV analog sensing circuits. In the SPICE simulations, the transient simulations of the output nodes of each analog block are demonstrated in the Fig. 10. As displayed, the sensing signal can be successfully obtained. The final close-loop gain of the proposed CTV analog sensing circuits is around 20.

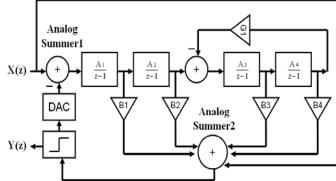

### B. 4-Stage Sigma-Delta Modulator

Considering digital conversion of 14 bits resolution, the design of sigma-delta modulator (SDM) is selected. Several different modulators have been used to achieve high

Fig. 10. SPICE transient results of the capacitance to voltage converter, chopper, Gm-C low-pass filter, and the gain amplifier. The nominal capacitance of the  $C_1$  is 200 fF and  $\Delta C$  is 2 aF. The signal frequency is 1 kHz and the chopping frequency is 200 kHz.

resolution, such as multi-loop cascade, multibit, high-order single-loop single-bit, etc [33]. In this work, a high-order single-loop single-bit architecture is chosen. The structure is attractive due to the high signal-to-noise ratio (SNR) and simple implementation. The oversampling ratio (OSR) and loop order n should be decided. For the single-bit architecture, the relationship between the dynamic range (DR) and OSR becomes

$$DR = \frac{3}{2} \left(\frac{2n+1}{\pi^{2n}}\right) OSR^{2n+1}.$$

(6)

In order to consider the degradation of the achievable DR [33] and circuit non-idealities, an OSR of 256 and n of 4 are chosen.

The proposed sigma-delta modulator consists of four integrators, two analog summers, an one-bit DAC, a quantizer, and gain circuits. The gain circuits provide feedforward gain  $B_1$  to  $B_4$  and feedback gain  $G_1$  as displayed in Fig. 11. The noise transfer function (NTF) of the proposed sigma-delta modulator is obtained by employing signal flow graph (SFG) and derived as

$$NTF(Z) = \frac{1}{\left\{ \begin{array}{l} 1 + A_1 B_1(\frac{1}{Z-1}) + (A_3 A_4 G_1 + A_1 A_2 B_2)(\frac{1}{Z-1})^2 \\ + (A_1 A_3 B_1 B_4 G_1 + A_1 A_2 A_3 B_3)(\frac{1}{Z-1})^3 \\ + (A_1 A_2 A_3 A_4 B_4 + A_1 A_2 A_3 A_4 B_2 G_1)(\frac{1}{Z-1})^4 \end{array} \right\}}$$

(7)

where  $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$ ,  $B_1$ ,  $B_2$ ,  $B_3$ ,  $B_4$ , and  $G_4$ , are coefficients of the proposed sigma-delta modulator. With

Fig. 11. The topology of the proposed sigma-delta modulator for the digitized capacitive transducer.

careful filter design, a Butterworth high-pass NTF is obtained as

$$NTF_{\text{butterworth}}(Z) = \frac{1}{\left\{ \begin{array}{c} 1 + 0.0583(\frac{1}{Z-1}) + 0.2687(\frac{1}{Z-1})^2 \\ + 0.0672(\frac{1}{Z-1})^3 \\ + 0.0051(\frac{1}{Z-1})^4 \end{array} \right\}}$$

(8)

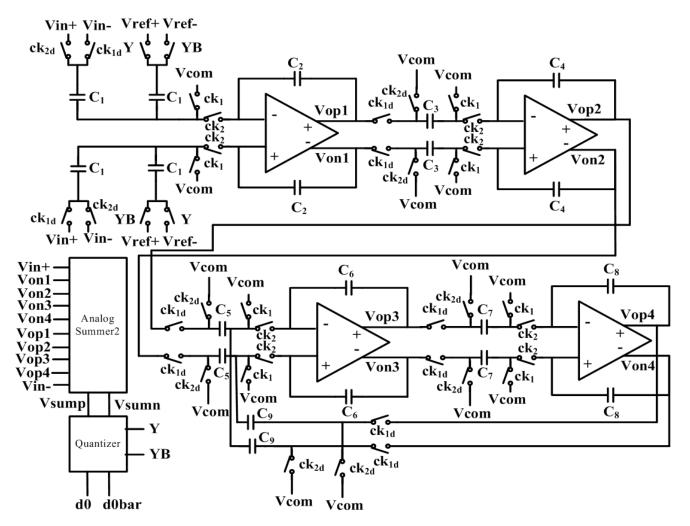

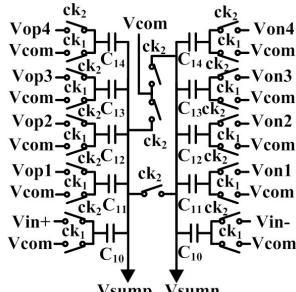

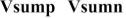

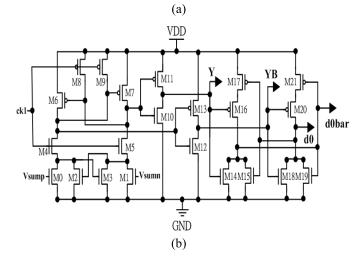

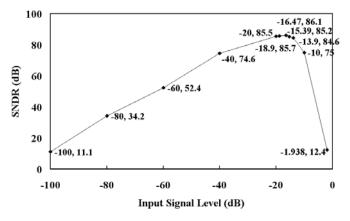

By using MATLAB to perform the behavior simulations of the NTF<sub>butterworth</sub> (Z), the poles of the NTF<sub>butterworth</sub> (Z) are all located inside the unit circle, which are  $0.8167 \pm 0.4804i$ and  $0.8912 \pm 0.044i$ . Thus, it analyzes in ensuring stability. By mapping (7) and (8), the coefficients of  $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$ , B<sub>1</sub>, B<sub>2</sub>, B<sub>3</sub>, B<sub>4</sub>, and G<sub>4</sub> are 0.166, 0.35, 0.25, 0.1, 5, 4.6, 3.8, 3.4, and 0.0166, respectively. The circuit implementations of the proposed sigma-delta modulator is built and demonstrated in Fig. 12. The entire circuit is implemented in switchedcapacitor (SC) networks. In the modulator, the OP is the main building block which determines the main performance and consumes most of the current of the whole circuits. The folded-cascaded OP shown in Fig. 13 is designed. The SC common-mode feedback (SC CMFB) is used due to its simplicity and efficiency in current consumption. To avoid signal dependent charge injection, non-overlapping clock signals are used. Instead of OP-based analog summer, the SC-based analog summer can reduce power consumption, and the circuit is implemented as shown in Fig. 14(a). Besides, the quantizer is displayed in Fig. 14(b). SPICE simulations are performed to obtain the output codes of the proposed sigma-delta modulator. These digital codes are used to calculate the signal-tonoise-plus-distortion ratio (SNDR) of the modulator through dedicated MATLAB programs. The dedicated programs are to perform fast Fourier transform (FFT) from these obtained codes. These codes are to calculate the signal power and noise power from the FFT data, and finally are to calculate the value of the SNDR. After performing MATLAB simulations, Fig. 15 shows the SNDR versus the input signal level. The DR is 98 dB and the peak SNDR is 86.1 dB. The effective resolution is equal to 14 bits, which is calculated as (86.1-1.76)/6.02 =14 bits.

Fig. 12. The whole circuit schematic of the proposed sigma-delta modulator.

Fig. 13. The circuit schematic of the folded-cascaded OP used in the proposed sigma-delta modulator.

## C. The Whole System

All the circuit blocks are integrated into the proposed digitized vibration detector. The output signals of the proposed

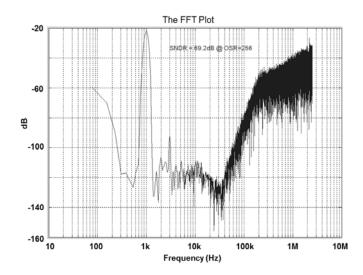

CTV analog sensing circuits are inputted into the 4-stage deltasigma modulator. In Fig. 16, the peak SNDR is around 69.2 dB under the nominal capacitance of the  $C_1$  of 600 fF and  $\Delta C$ of 1.2 fF. The signal frequency is 1 kHz and the chopping frequency is 200 kHz. The effective resolution is equal to 11.2 bits. All the functions and performance of the proposed digitized vibration detector are successfully tested and proven through SPICE simulations.

## **IV. MEASUREMENT RESULTS**

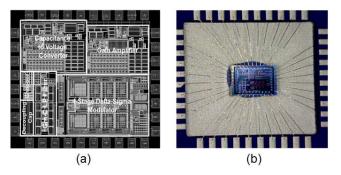

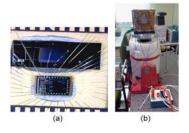

17 demonstrates the physical layout Fig. and microphotograph of the proposed CMOS digitized capacitive transducer. The area of the proposed CMOS digitized capacitive transducer is  $1812 \times 1420 \ \mu m^2$  and the power consumption including digital buffers is 18 mW. Fig. 18 shows the proposed digitized vibration detector and measurement setup. The measurement setup includes power supplies, a LDS V40B electrodynamic shaker, a Tektronix-TDS1012B oscilloscope, a Tektronix-3022B signal generator, an Agilent-33522A function generator, an Agilent-35670 dynamic signal analyzer, and the proposed chip. Firstly, the shaker is excited by the signal generator. In the measurement, the frequency of shaker is fixed at 100 Hz. The function generator is used to

Fig. 14. The circuit schematic of (a) analog summer and (b) quantizer.

Fig. 15. The SNDR versus input signal level.

generate the chopping frequency and the sampling frequency. The chopping and sampling frequency are fixed at 200 kHz and 5 MHz, respectively. The dynamic characteristic of the shaker is also monitored by a commercial accelerometer

Fig. 16. The output spectrum of the proposed digitized vibration detector. The nominal capacitance of the  $C_1$  is 600 fF and  $\Delta C$  is 1.2 fF. The signal frequency is 1 kHz and the chopping frequency is 200 kHz.

Fig. 17. The (a) physical layout and (b) microphotograph of the proposed CMOS digitized capacitive transducer.

Fig. 18. (a) The proposed digitized vibration detector and (b) the measurement setup.

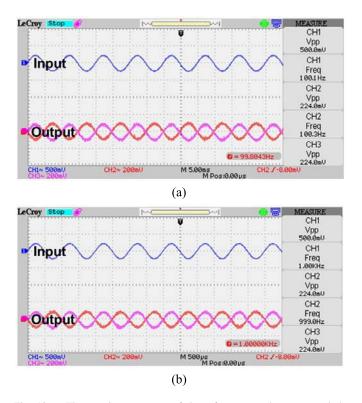

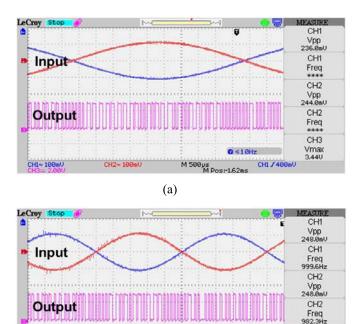

PCB-J352C34. After exciting the shaker, the sensing signal of the proposed digitized vibration detector is measured to analyze the transient and frequency response. The transient responses of the reference accelerometer and the proposed CTV analog sensing circuits with excitation of 2.5g intensity are shown in Fig. 19, respectively. The upper waveform is the output of reference accelerometer, and the lower waveform is the output of the proposed CTV analog sensing circuits. Measured results of digitized stream output with excitation of 2.5g intensity are displayed in Fig. 20. As proven, the digitized stream output is correctly pulse-density modulated. In Fig. 21, the frequency response is measured under excitation of 1g intensity. As displayed, the capacitance variations of the in-plane SOI accelerometer are successfully

Fig. 19. The transient response of the reference accelerometer and the proposed CTV analog sensing circuits with excitation of 2.5 g intensity. The frequency of shaker is (a) 100 Hz and (b) 1 kHz.

Fig. 20. Measured results of digitized stream output with excitation of 2.5 g intensity. The frequency of shaker is (a) 100 Hz and (b) 1 kHz.

(b)

CH1~ 100ml

M 100ps M Pos:-1 CH3 Vmax 3.440

0<10Hz

CH1 / 40

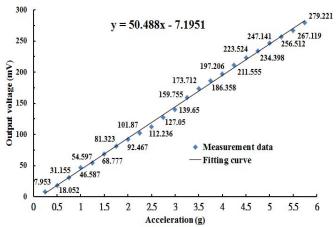

converted into voltage variations by the proposed TV analog sensing circuits. All the measured outputs of the proposed CTV analog sensing circuits are plotted in Fig. 22. The

Fig. 21. The frequency response of the proposed digitized vibration detector. The frequency of shaker is 100 Hz and is also with excitation of 1g intensity.

Fig. 22. The sensitivity of the proposed digitized vibration detector under shaking frequency of 100 Hz and excitation of 1g intensity.

sensitivity is 50.488 mV/g over the excitation of 0.25 to 5.75g intensity. In addition, the noise floor is determined from [11]

Noise floor =

$$\frac{output \ noise}{sensitivity} \times (\frac{1}{\sqrt{bandwidth}})$$

(9)

where the output noise and the bandwidth are measured by the dynamic signal analyzer. The output noise and bandwidth are 46.56  $\mu$ V and 1 Hz, respectively. By (9), the noise floor is 0.922 mg/Hz<sup>1/2</sup>. Moreover, maximum nonlinearity is derived as [34]

$$Maximum non-linearity = \frac{maximum deviation (V)}{full scale output (V)} \times 100\%.$$

(10)

By (10), maximum nonlinearity is 2.5% over the excitation of 0.25 to 5.75g intensity. In Fig. 23, the cross-axis sensitivities in the Y-axis and Z-axis are measured under excitation of 1g intensity. The cross-axis Y sensitivity and cross-axis Z sensitivity are less than 1.7% and 1.66%, respectively.

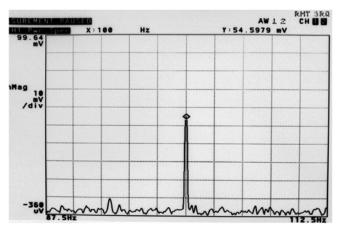

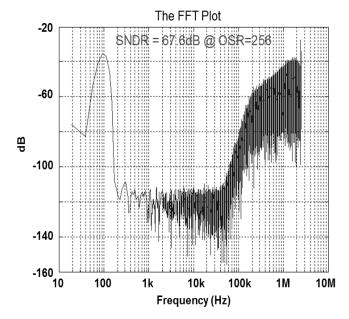

Finally, measured results of the peak SNDR of the proposed digitized vibration detector are shown in Fig. 24. The peak

SUMMARY ON THE CHARACTERISTICS OF THE PROPOSED DIGITIZED VIBRATION DETECTOR

IEEE SENSORS JOURNAL, VOL. 14, NO. 8, AUGUST 2014

| Technology                                                                  | 0.35 µm CMOS 2P4M          |  |  |

|-----------------------------------------------------------------------------|----------------------------|--|--|

| Power supply                                                                | 3.0 V                      |  |  |

| Power consumption                                                           | 18 mW                      |  |  |

| Chopping frequency                                                          | 200 kHz                    |  |  |

| Sampling frequency                                                          | 5 MHz                      |  |  |

| OSR                                                                         | 256                        |  |  |

| Measured signal bandwidth                                                   | <10 kHz                    |  |  |

| Measured range                                                              | 0.25-5.75 g                |  |  |

| Sensitivity                                                                 | 50.488 mV/g                |  |  |

| Maximum nonlinearity                                                        | 2.5%                       |  |  |

| Maximum cross-axis Y sensitivity                                            | 1.7%                       |  |  |

| Maximum cross-axis Z sensitivity                                            | 1.66%                      |  |  |

| Noise floor                                                                 | 0.922 mg/Hz <sup>1/2</sup> |  |  |

| Measured peak SNDR of the<br>proposed chip with Z-axis SOI<br>accelerometer | 67.6 dB @ 3.25g            |  |  |

| Physical layout area                                                        | $1812\times1420\;\mu m^2$  |  |  |

| Application field                                                           | Micro-accelerometers       |  |  |

same. That implies that the proposed CMOS digitized capacitive transducer and in-plane SOI accelerometer are robustly and compactly combined together. Thus, all the functions and performance between simulations and measurements can successfully match each other. Compared with [17]–[22], the output type of this work is digital. However, the whole noise floor of this work is higher than other works. That is because more back-end signal processing circuits are added in this work. Thus, more noise coming from circuits must be also generated. Although the sensitivity of this work is not as large as previous works, it can be adjusted by the gain of gain amplifier. The characteristics of the proposed CMOS digitized vibration detector are summarized in Table II.

## V. CONCLUSION

A digitized vibration detector implemented by CMOS digitized capacitive transducer with in-plane SOI accelerometer is newly proposed. All the functions and performance of the proposed CMOS digitized vibration detector are successfully tested and proven through measurements. The core functionalities of the proposed digitized vibration detector are successfully obtained and may be applied to the automobiles and consumer products. In the future, the developed techniques are adaptively designed into digitized accelerometer applications.

# ACKNOWLEDGMENT

The authors would like to thank C.-R. Peng for his help in the measurement setup.

### REFERENCES

- H. Qu, D. Fang, and H. Xie, "A single-crystal silicon 3-axis CMOS-MEMS accelerometer," in *Proc. IEEE Sensors Conf.*, Oct. 2004, pp. 661–664.

- [2] H. Takao, Y. Matsumoto, H. See, and M. Ishida, "A monolithically integrated three-axis accelerometer using CMOS compatible stresssensitive differential amplifiers," *IEEE Trans. Electron Devices*, vol. 46, no. 1, pp. 109–116, Jan. 1999.

Fig. 23. The cross-axis (a) Y and (b) Z sensitivity of the proposed digitized vibration detector under shaking frequency of 100 Hz and excitation of 1 g intensity.

Fig. 24. Measured results of the peak SNDR of the proposed digitized vibration detector. The peak SNDR is 67.6 dB under shaking frequency of 100 Hz and excitation of 3.25g intensity.

SNDR is 67.6 dB under excitation of 3.25g intensity. The effective resolution is 11 bits. Compared with simulation results in section II, the effective resolution is almost the

- [3] B. Chen, J. Miao, C. K. Lim, F. E. H. Tay, and C. Iliescu, "Dynamic behavior of high-G MEMS accelerometer incorporated with novel micro-flexures," *Int. J. Softw. Eng. Knowl. Eng.*, vol. 15, no. 2, pp. 225–230, Apr. 2005.

- [4] H. Takao, Y. Matsumoto, H. See, M. Ishida, and T. Nakamura, "Analysis and design considerations of three-dimensional vector accelerometer using SOI structure for wide temperature range," *Sens. Actuators A, Phys.*, vol. 55, nos. 2–3, pp. 91–97, Jul. 1996.

- [5] C. M. Sun, M. H. Tsai, Y. C. Liu, and W. Fang, "Implementation of a monolithic single proof-mass tri-axis accelerometer using CMOS-MEMS technique," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1670–1679, Jul. 2010.

- [6] K. I. Lee, H. Takao, K. Sawada, and M. Ishida, "Low temperature dependence three-axis accelerometer for high temperature environments with temperature control of SOI piezoresistors," *Sens. Actuators A*, *Phys.*, vol. 104, no. 1, pp. 53–60, Mar. 2003.

- [7] C. Iliescu and J. Miao, "One-mask process for silicon accelerometers on Pyrex glass utilising notching effect in inductively coupled plasma DRIE," *Electron. Lett.*, vol. 39, no. 8, pp. 658–659, Apr. 2003.

- [8] L. M. Roylance and J. B. Angell, "A batch-fabricated silicon accelerometer," *IEEE Trans. Electron Devices*, vol. 26, no. 12, pp. 1911–1917, Dec. 1979.

- [9] C.-K. Chan, S.-C. Lo, Y.-C. Huang, M. Wu, M.-Y. Wang, and W. Fang, "Poly-Si based two-axis differential capacitive-sensing accelerometer," *IEEE Sensors J.*, vol. 12, no. 12, pp. 3301–3308, Dec. 2012.

- [10] M.-H. Tsai, Y.-C. Liu, and W. Fang, "A three-axis CMOS-MEMS accelerometer structure with vertically integrated fully differential sensing electrodes," *J. Microelectromech. Syst.*, vol. 21, no. 6, pp. 1329–1337, Dec. 2012.

- [11] C.-P. Hsu, M.-C. Yip, and W. Fang, "Implementation of a gap-closing differential capacitive sensing Z-axis accelerometer on an SOI wafer," *J. Micromech. Microeng.*, vol. 19, no. 7, pp. 1–7, Jul. 2009.

- [12] A. Partridge, J. K. Reynolds, B. W. Chui, E. M. Chow, A. M. Fitzgerald, L. Zhang, *et al.*, "A high-performance planar piezoresistive accelerometer," *J. Microelectromech. Syst.*, vol. 9, no. 1, pp. 58–66, Mar. 2000.

- [13] B. Puers and W. Sansen, "A new uniaxial accelerometer in silicon based on the piezojunction effect," *IEEE Trans. Electron Devices*, vol. 35, no. 6, pp. 764–770, Jun. 1988.

- [14] P. Scheeper, J. O. Gulloy, and M. Kofoed, "A piezoelectric triaxial accelerometer," J. Micromech. Microeng., vol. 6, no. 1, pp. 131–133, 1996.

- [15] T. Storgaard-Larsen, S. Bouwstra, and O. Leistiko, "Optomechanical accelerometer based on strain sensing by a Bragg grating in a planar waveguide," *Sens. Actuators A, Phys.*, vol. 52, nos. 1–3, pp. 25–32, Apr. 1996.

- [16] C. H. Liu, A. M. Barzilai, J. K. Reynolds, A. Partridge, T. W. Kenny, J. D. Grade, *et al.*, "Characterization of a high-sensitivity micromachined tunneling accelerometer with micro-G resolution," *J. Microelectromech. Syst.*, vol. 7, no. 2, pp. 235–244, Jun. 1998.

- [17] M. Lemkin and B. E. Boser, "A three-axis micromachined accelerometer with a CMOS position-sense interface and digital offset-trim electronics," *IEEE J. Solid-State Circuits*, vol. 34, no. 4, pp. 456–468, Apr. 1999.

- [18] J. Wu, G. K. Fedder, and L. R. Carley, "A low-noise low-offset capacitive sensing amplifier for 50-μg/√Hz monolithic CMOS MEMS accelerometer," *IEEE J. Solid-State Circuits*, vol. 39, no. 5, pp. 722–730, May 2004.

- [19] H. Qu, D. Fang, and H. Xie, "A monolithic CMOS-MEMS 3-axis accelerometer with a low-noise, low-power dual-chopper amplifier," *IEEE Sensors J.*, vol. 8, no. 9, pp. 1511–1518, Sep. 2008.

- [20] K. T. C. Chai, D. Han, R. P. Singh, D. D. Pham, C. Y. Pang, J. W. Luo, *et al.*, "118-dB dynamic range, continuous-time openedloop capacitance to voltage converter readout for capacitive MEMS accelerometer," in *Proc. Asian Solid-State Circuits Conf.*, Nov. 2010, pp. 1–4.

- [21] H. Sun, D. Fang, K. Jia, F. Maarouf, H. Qu, and H. Xie, "A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers," *IEEE Sensors J.*, vol. 11, no. 4, pp. 925–933, Apr. 2011.

- [22] S. S. Tan, C. Y. Liu, L. K. Yeh, Y. H. Chiu, M. S. C. Lu, and K. Y. J. Hsu, "An integrated low-noise sensing circuit with effect bias stabilization for CMOS MEMS capacitive accelerometers," *IEEE Trans. Circuits Syst.*, *I, Reg. Papers*, vol. 58, no. 11, pp. 2661–2672, Nov. 2011.

- [23] C. Lu, M. Lemkin, and B. E. Boser, "A monolithic surface micromachined accelerometer with digital output," *IEEE J. Solid-State Circuits*, vol. 30, no. 12, pp. 1367–1373, Dec. 1995.

- [24] H. Kulah, J. Chae, N. Yazdi, and K. Najafi, "A multi-step electromechanical ΔΣ converter for micro-g capacitive accelerometers," in *Proc. IEEE ISSCC*, Feb. 2003, pp. 202–203.

- [25] B. V. Amini and F. Ayazi, "A 2.5-V 14-bit ΣΔ CMOS SOI capacitive accelerometer," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2467–2476, Dec. 2004.

- [26] V. P. Petkov and B. E. Boser, "A fourth-order ΣΔ interface for micromachined inertial sensors," *IEEE J. Solid-State Circuits*, vol. 40, no. 8, pp. 1602–1609, Aug. 2005.

- [27] H. Kulah, J. Chae, N. Yazdi, and K. Najafi, "Noise analysis and characterization of a sigma-delta capacitive microaccelerometer," *IEEE J. Solid-State Circuits*, vol. 41, no. 2, pp. 352–361, Feb. 2006.

- [28] B. V. Amini, R. Abdolvand, and F. Ayazi, "A 4.5-mW closed-loop microgravity CMOS SOI accelerometer," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2983–2991, Dec. 2006.

- [29] M. Paavola, M. Kämäräinen, J. A. M. Järvinen, M. Saukoski, M. Laiho, and K. A. I. Halonen, "A micropower interface ASIC for a capacitive 3-axis micro-accelerometer," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2651–2665, Dec. 2007.

- [30] L. He, Y. P. Xu, and M. Palaniapan, "A CMOS readout circuit for SOI resonant accelerometer with 4-μg bias stability and 20-μg/√Hz resolution," *IEEE J. Solid-State Circuits*, vol. 43, no. 6, pp. 1480–1490, Jun. 2008.

- [31] M. Yücetas, M. Pulkkinen, A. Kalanti, J. Salomaa, L. Aaltonen, and K. Halonen, "A high-resolution accelerometer with electrostatic damping and improved supply sensitivity," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1721–1730, Jul. 2012.

- [32] Z. Ye, H. Yang, T. Yin, G. Huang, and F. Liu, "High-performance closedloop interface circuit for high-Q capacitive microaccelerometers," *IEEE Sensors J.*, vol. 13, no. 5, pp. 1425–1433, May 2013.

- [33] R. Schreier and G. C. Temes, Understanding Delta-sigma Data Converters. New Work, NY, USA: IEEE Press, 2004.

- [34] AN012 Accelerometer Errors [Online]. Available: http://www. kionix.com/sites/default/files/AN012%20Accelerometer%20Errors.pdf

**Cheng-Ta Chiang** (S'00–M'05–SM'13) was born in Taiwan, in 1977. He received the B.S. degree in electronics engineering from Chung Yuan Christian University, Jhongli, Taiwan, in 1999, the M.S. degree in biomedical engineering from National Cheng Kung University, Tainan, Taiwan, in 2001, and the Ph.D. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2006.

He was a Visiting Scholar with the Department of Electrical and Computer Engineering, The Johns

Hopkins University, Baltimore, MD, USA, from 2004 to 2005. He was included in *Marquis Who's Who in Science and Engineering* from 2006 to 2007 and *Marquis Who's Who in the World* in 2008. Since 2007, he has been a Review Committee Member of the National Chip Implementation Center, Hsinchu. From 2006 to 2010, he was a Member of Technical Staff with the Industrial Technology Research Institute, Hsinchu, and was responsible for Nyquist & Oversampled A/D converters, and MEMS circuits. Since 2010, he has been with National Chia Yi University, Chiayi, Taiwan, and is currently an Associate Professor with the Department of Electrical Engineering. His main research interests include analog integrated circuits, biomedical electronics, image sensor circuits and systems, sensor signal conditioning and transducers, Nyquist A/D converters, and high-resolution DT and CT delta-sigma modulator.

Dr. Chiang is an IEEE conference reviewer servicing for 12MTC 2008, ISIEA from 2009 to 2012, PECON 2010 and 2012, IAPEC from 2011 to 2012, ICEDSA from 2011 to 2012, ICEDSA from 2011 to 2012, ICEDEIA from 2011 to 2012, PEOCO from 2011 to 2013, CSNT from 2011 to 2012, SCORED from 2011 to 2012, BEIAC 2012, ISBEIA 2012, IECON 2013, CHUSER 2014, ISIE 2014, and a Journal Reviewer for the IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, the IEEE TRANSACTIONS ON INDUSTRIAL ELEC-TRONICS, the IEEE SENSORS JOURNAL, the *IET Journal of Engineering, Microelectronics Journal*, the *EURASIP Journal on Advanced in Signal Processing*, and an Editorial Advisory Board Member for the Sensors and Transducers Journal. He is an IEEE Conference Session Chair servicing for the IEEE ISIEA 2011 and 2012, IEEE Sensors 2012, IEEE ISIE 2013, and IEEE ICMA 2013.

**Chun-I Chang** was born in Taipei, Taiwan, in 1983. He received the M.S. degree from the Mechanical Engineering Department, National Chiao-Tung University, Hsinchu, Taiwan, in 2008. He is currently pursuing the Ph.D. degree at the Institute of Nanoengineering and Microsystems, National Tsing Hua University.

His major research interests include CMOS MEMS magnetic sensors and inertial sensors, and sensors integration.

Weileun Fang (M'06–SM'11) was born in Taipei, Taiwan. He received the Ph.D. degree from Carnegie Mellon University, Pittsburgh, PA, USA, in 1995. His doctoral research focused on the determining of the mechanical properties of thin films using micromachined structures. In 1995, he was a Post-Doctoral Research with the Synchrotron Radiation Research Center, Hsinchu, Taiwan. He joined the Power Mechanical Engineering Department, National Tsing Hua University, Hsinchu, in 1996, where he is currently a Professor as well as a Faculty

Member with the NEMS Institute. In 1999, he was with the California Institute of Technology, Pasadena, CA, USA, as a Visiting Associate, under the supervision of Prof. Y.-C. Tai. His current research interests include MEMS with emphasis on micro fabrication/packaging technologies, CMOS MEMS, CNT MEMS, micro optical systems, micro sensors and actuators, and characterization of thin film mechanical properties.

He is currently the Editorial Board Member of the *Journal of Micromechanics and Microengineering* and the IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY and an Associate Editor of the IEEE SENSORS JOURNAL and the *Journal of Micro/Nanolithography, MEMS*, and *MOEMS*. He has been serves as the Chief Delegate of Taiwan to the World Micromachine Summit in 2012. He served on the Technical Program Committee (TPC) of the IEEE MEMS in 2007, and the Executive Program Committee of Transducers in 2007, and the Executive Program Committee of Transducers from 2009 to 2013. He has been a member of the International Steering Committee of Transducers since 2009. He serves as a Technical Consultant for many MEMS companies in Taiwan.